- 您现在的位置:买卖IC网 > Sheet目录3889 > PIC18C452T-E/L (Microchip Technology)IC MCU OTP 16KX16 A/D 44PLCC

PIC18CXX2

DS39026C-page 136

2001 Microchip Technology Inc.

14.4.5

BAUD RATE GENERATOR

In I2C Master mode, the reload value for the BRG is

located in the lower 7 bits of the SSPADD register

(Figure 14-14). When the BRG is loaded with this

value, the BRG counts down to 0 and stops until

another reload has taken place. The BRG count is dec-

remented twice per instruction cycle (TCY) on the Q2

and Q4 clocks. In I2C Master mode, the BRG is

reloaded automatically. If Clock Arbitration is taking

place, for instance, the BRG will be reloaded when the

SCL pin is sampled high (Figure 14-15).

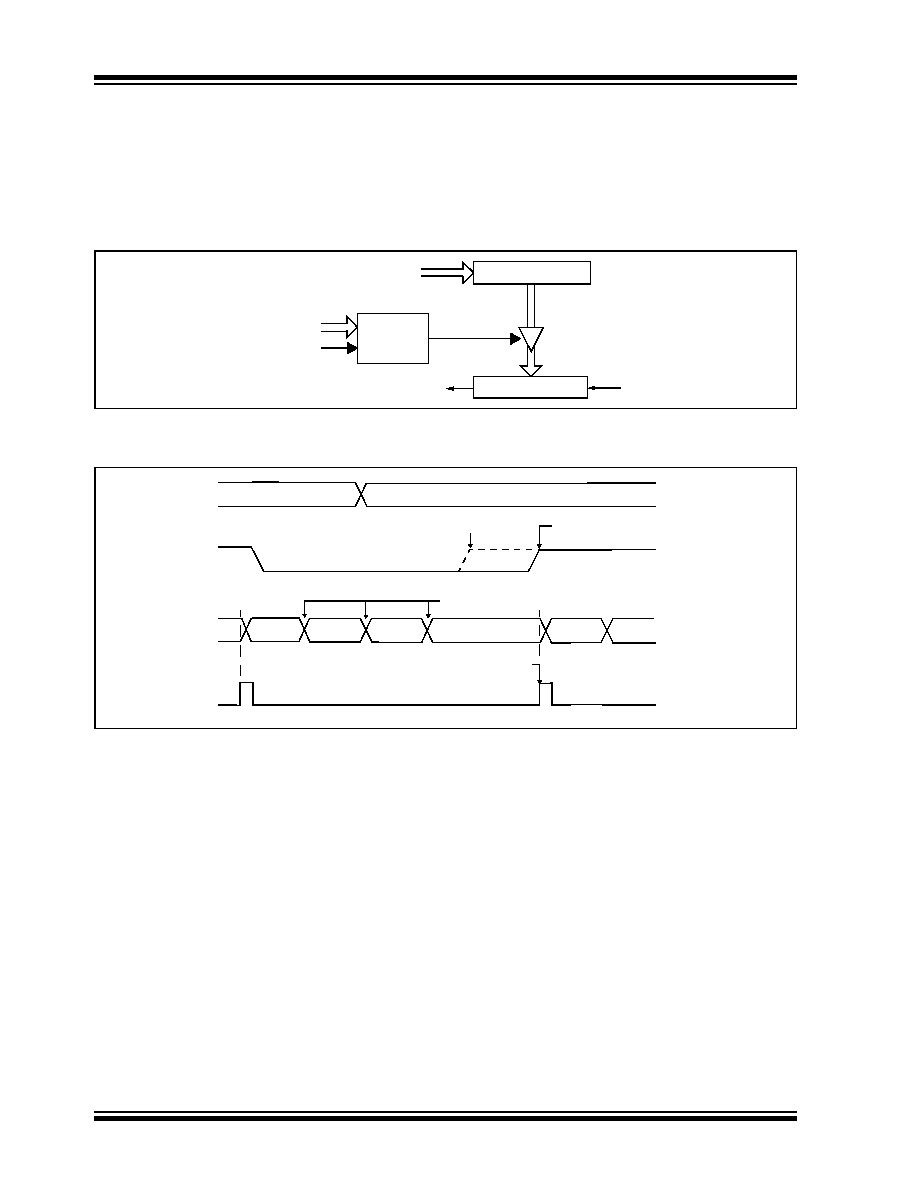

FIGURE 14-14:

BAUD RATE GENERATOR BLOCK DIAGRAM

FIGURE 14-15:

BAUD RATE GENERATOR TIMING WITH CLOCK ARBITRATION

SSPM3:SSPM0

BRG Down Counter

CLKOUT

FOSC/4

SSPADD<6:0>

SSPM3:SSPM0

SCL

Reload

Control

Reload

SDA

SCL

SCL de-asserted but slave holds

DX-1

DX

BRG

SCL is sampled high, reload takes

place and BRG starts its count.

03h

02h

01h

00h (hold off)

03h

02h

Reload

BRG

Value

SCL low (clock arbitration)

SCL allowed to transition high

BRG decrements on

Q2 and Q4 cycles

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC16C54C-40/SS

IC MCU OTP 512X12 20SSOP

22-15-3033

CONN FFC/FPC 3POS .100 RT ANG

PIC18LC858T-I/PT

IC MCU OTP 16KX16 CAN 80TQFP

22-02-3033

CONN FFC/FPC VERTICAL 3POS .100

PIC18C858T-E/PT

IC MCU OTP 16KX16 CAN 80TQFP

PIC18C858T-I/PT

IC MCU OTP 16KX16 CAN 80TQFP

PIC18C658T-I/PT

IC MCU OTP 16KX16 CAN 64TQFP

PIC16LC717T-E/SS

IC MCU OTP 2KX14 A/D PWM 20SSOP

相关代理商/技术参数

PIC18C452T-E/PT

功能描述:8位微控制器 -MCU 32KB 1536 RAM 34I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C452T-I/L

功能描述:8位微控制器 -MCU 32KB 1536 RAM 34I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C452T-I/PT

功能描述:8位微控制器 -MCU 32KB 1536 RAM 34I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C601-I/L

功能描述:8位微控制器 -MCU 256KB 1536 RAM 26I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C601-I/L021

制造商:Microchip Technology Inc 功能描述:

PIC18C601-I/PT

功能描述:8位微控制器 -MCU 256KB 1536 RAM 26I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C601T-I/L

功能描述:8位微控制器 -MCU 256KB 1536 RAM 26I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18C601T-I/PT

功能描述:8位微控制器 -MCU 256KB 1536 RAM 26I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT